Sil9678 HDMI Transmitter with HDCP 2.2

# Support

# **Data Sheet**

Sil-DS-1142-B

April 2014

#### **Copyright Notice**

Copyright © 2012-2014 , Inc. All rights reserved. The contents of these materials contain proprietary and information (including trade secrets, copyright, and other Intellectual Property interests) of , Inc. or its affiliates. All rights are reserved and contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of , Inc. or its affiliates. You may not these materials except for your bona fide non-commercial evaluation of your potential purchase of products and/or services from or its affiliates; and in connection with your purchase of products or services from or its affiliates, and in accordance with the terms and conditions stipulated. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of, distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### **Patents**

The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by , Inc. or its affiliates.

#### **Trademark Acknowledgment**

<sup>®</sup>, the logo, Instaport<sup>®</sup>, the Instaport logo, InstaPrevue<sup>®</sup>, Simplay<sup>®</sup>, Simplay HD<sup>®</sup>, the Simplay HD logo, Simplay Labs™, the

Simplay Labs logo, UltraGig™, the UltraGig logo are trademarks or registered trademarks of , Inc. in the United States or other countries. HDMI and the HDMI logo with High-Definition Multimedia Interface are trademarks or registered trademarks of, and are d under license from, HDMI Licensing, LLC. in the United States or other countries. MHL® and the MHL logo with Mobile High-Definition Link are trademarks or registered trademarks of, and are d under license from, MHL, LLC. in the United States or other countries. WirelessHD®, the WirelessHD logo, WiHD and the WiHD logo are trademarks, registered trademarks or service marks of SiBeam, Inc. in the United States or other countries.

HDMI Licensing, LLC; MHL, LLC; Simplay Labs, LLC; and SiBeam, Inc. are wholly owned subsidiaries of , Inc..

All other trademarks and registered trademarks are the property of their respective owners in the United States or other countries. The absence of a trademark symbol does not constitute a waiver of 's trademarks or other intellectual property rights with regard to a product name, logo or slogan.

#### **Export Controlled Document**

This document contains materials subject to the Export Administration Regulations. Transfer of this information by any means to a foreign destination may require a license. These materials shall not, in the absence of authorization under U.S. and local law and regulations, as required, be d by or

These materials are provided on an "AS IS" basis. , Incanditsaffiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non(iii) any party engaged in nuclear, chemical/biological weapons or missile proliferation activities; or (iv) any party for in the design, development,

or production of rocket systems or unmanned air vehicles.

#### **Further Information**

To request other materials, documentation, and information, contact your local, Inc. sales office or visit the, Inc. web site at www..com.

#### Disclaimers

infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or

results provided in, or that may be obtained from of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Inc. and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update of keep courset the information contained in these materials, and expressly objective distained all direct, indirect, possely, indirect, consequential, reliance and punitive dismages, and to add to, developed and the content of these materials. Inc. and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, developed and to add to, developed and the content of the production of

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by , Inc. and/or its affiliates are provided on "AS IS" basis, except to the extent that , Inc. and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied).

EXCEPT FOR SUCH LIMITED WARRANTY, , INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY , INC. AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

## **Contents**

| 1. | General Descriptio    | vi                                             | 6             |

|----|-----------------------|------------------------------------------------|---------------|

|    | 1.1.                  | HDMI Irput                                     | 6             |

|    | 1.2.                  | HDMI Output                                    | 6             |

|    | 1.3.                  | Features                                       | 6             |

|    | 1.4.                  | Packaging                                      | 6             |

|    | 1.5.                  | Pin Diagram                                    | 7             |

| 2. | Functional Descrip    |                                                | 8             |

|    | 2.1.                  | HDMI Input Interface                           | 8             |

|    | 2.2.                  | Video Data Conversion Logic Block              | 10            |

|    | 2.2.1.                | •                                              | 10            |

|    |                       | Color Space Converters                         | 10            |

|    |                       |                                                |               |

|    | 2.2.2.<br>2.2.3.      |                                                | <br>          |

|    |                       | •                                              | 11            |

|    |                       | o 4:4:4 Upsampler                              |               |

|    | 2.2.5.<br>2.2.6.      | No rungi cipinani                              | 11<br>11      |

|    | 2.2.0.                |                                                |               |

|    |                       | Receiver HDCP 1.4 Authentication Logic Block   |               |

|    |                       | HDCP 1.4 Decryption Engine Block               | 11            |

|    |                       | Transmitter HDCP Authentication Logic Block    | 44            |

|    | 2.6.                  | HDCP 1.4/2.2 Encryption Engine Block           |               |

|    | 2.7.                  | Add TaleStreether But                          |               |

|    |                       | One-Time Programmable Block                    | 12            |

|    |                       | Serial Peripheral Interface Logic Block        | 12            |

|    |                       | In-System-Program Block                        | 12            |

|    | 2.11.                 | Microcontroller Unit                           | 12            |

|    | 2.12.                 | Oxillar                                        | 12            |

|    |                       | Logic I <sup>2</sup> C Slave Logic Block       | 12            |

|    | 2.14.                 | Configuration, Status, and Interrupt Control L | ogic Block 13 |

|    | 2.15.                 | North.                                         | 14            |

|    |                       | DDC Master Block                               | 14            |

|    | 2.17.                 | On-Chip Regulation                             | 14            |

| 3. | Electric              | al Specifications                              | 15            |

|    | 3.1.                  | Absolute Maximum Conditions                    | 15            |

|    | 3.2.                  | Normal Operating Conditions                    | 16            |

|    | 3.2.1.                | =                                              | 17            |

|    | 3.2.2.                |                                                | 18            |

|    | 3.3.                  | on a consumption                               | 18            |

|    |                       | AC Specification  AC Timing Specifications     | 18            |

|    | 3.3.1. TWO            | one mining specifications                      |               |

|    | 3.3.3.                | ESD Specifications                             | 19            |

| 4. | Timing Diagrams       | ISO Specifications                             | 20            |

|    | 4.1.                  | RESETTN Timing Diagrams                        | 20            |

|    | 4.2.                  | Output Timing Diagrams                         | 20            |

| 5. |                       | Output Inning Diagrants                        | 21            |

|    | Pin Descriptions 5.1. |                                                | 21            |

|    | 5.2.                  | HDMI Input                                     | 21            |

|    | F 2                   | HDMI Output                                    | 22            |

|    | 5.4.                  | Edernal XTAL Pins                              | 22            |

|    | 5.5.                  | Control and Configuration Pins                 | 23            |

|    | 5.6.                  | Power and Ground Pins.                         | 25            |

| _  | J.U.                  | Reserved and Not Connected Pins                |               |

| 6. | Feature Inmation      |                                                | 25            |

|    | 6.1.                  | RGB to YCbCr Color Space Converter             | 25            |

|            | 6.2.      | YCbCr to RGB Color Space Converter                   | 25 |

|------------|-----------|------------------------------------------------------|----|

|            | 6.3.      | 3D Video mats                                        |    |

|            | 6.4.      | Device Address Configuration Using CI2CA/GPIO4/GPIO5 | 26 |

| 7.         | Desig     | n Recommendations                                    | 28 |

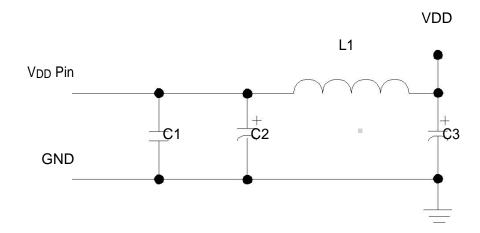

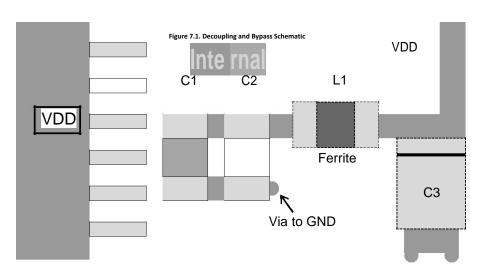

|            | 7.1.      | Power Supplies Decoupling                            | 28 |

|            | 7.2.      | High-speed TMDS Signals                              | 29 |

|            | 7.2.1.    |                                                      | 29 |

|            | 7.2.2.    | Transmitter Layout Guidelines                        | 29 |

|            | 7.2.3.    | ESD Protection                                       | 29 |

|            | 7.3.      | EMI Considerations                                   |    |

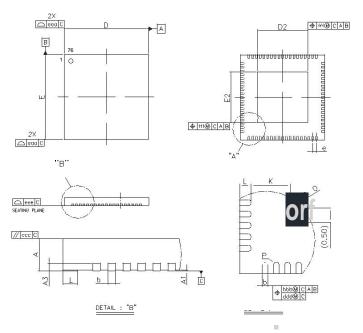

| 8.         | Packa     | ging                                                 | 30 |

|            | 8.1.      | ePad Requirements                                    |    |

|            | 8.2.      | Package Dimensions                                   | 31 |

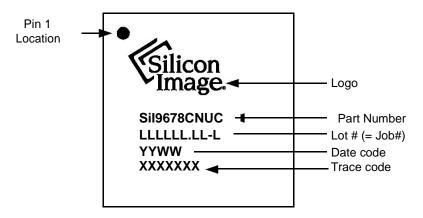

|            | 8.3.      | Marking Specification                                | 32 |

|            | 8.4.      | Ordering Inmation                                    |    |

| References |           |                                                      | 33 |

| 9          | Standar   | ds Documents                                         | 33 |

|            | Docum     | ents                                                 | 33 |

| Revisio    | n History |                                                      | 34 |

# **Figures**

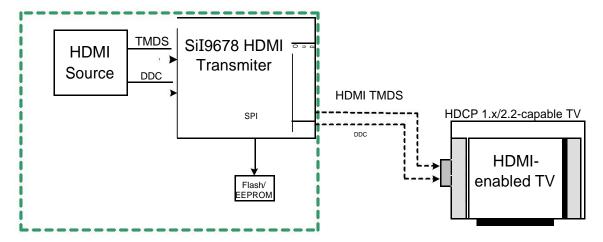

| Figure 1.1. Typical Application (Sil9678 HDMI Transmitter)              |    |

|-------------------------------------------------------------------------|----|

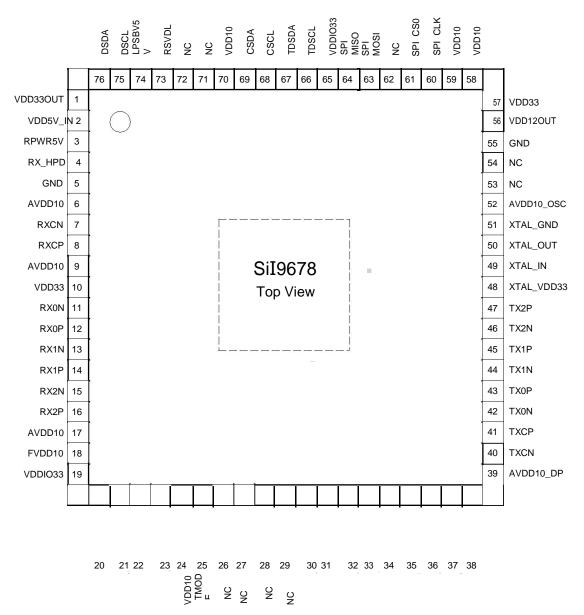

| Figure 1.2. Pin Diagram (Top View)                                      |    |

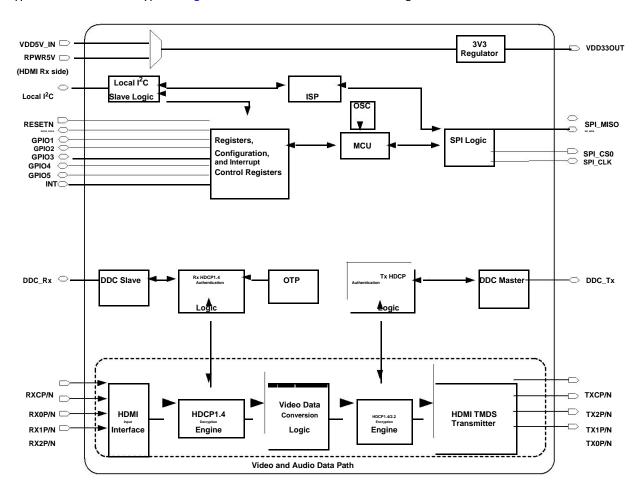

| Figure 2.1. Functional Block Diagram                                    |    |

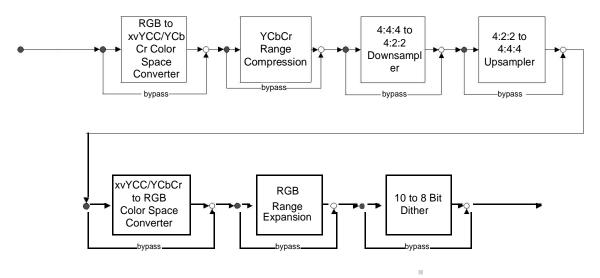

| Figure 2.2. Default Video Processing Path                               |    |

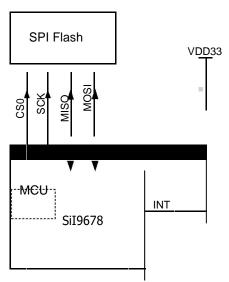

| Figure 2.3. Stand-alone Mode                                            |    |

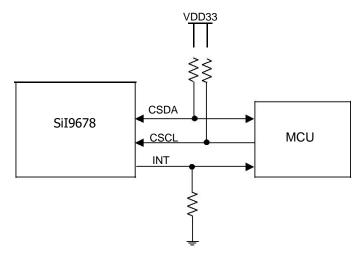

| Figure 2.4. External MCU Mode                                           |    |

| Figure 3.1. Test Point VDDTP VDD Noise Tolerance Specification          |    |

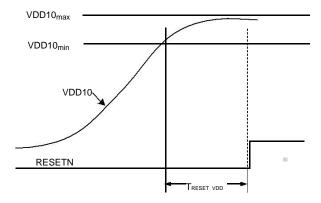

| Figure 4.1. Conditions of RESETN                                        | 20 |

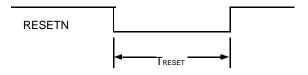

| Figure 4.2. RESETN Minimum Timings                                      |    |

| Figure 4.3. I <sup>2</sup> C Data Valid Delay (Driving Read Cycle Data) | 20 |

| Figure 4.4. INT Output Signal Response to Interrupt Condition           | 20 |

| Figure 7.1. Decoupling and Bypass Schematic                             |    |

| Figure 7.2. Decoupling and Bypass Capacitor Placement                   | 28 |

| Figure 7.2. Decoupling and Bypass Capacitor Placement                   | 31 |

|                                                                         |    |

# **Tables**

| Table 2.1. Supported 2D Video mats                                        |    |

|---------------------------------------------------------------------------|----|

| Table 3.1. Absolute Maximum Conditions                                    | 15 |

| Table 3.2. Normal Operating Conditions                                    | 16 |

| Table 3.3. DC Digital I/O Specifications                                  | 17 |

| Table 3.4. TMDS Input DC Specification                                    |    |

| Table 3.5. TMDS Output DC Specifications  Table 3.6. DC Power Consumption | 18 |

| Table 3.7. TMDS Input Timing AC Specifications                            |    |

| Table 3.8. TMDS Output Timings                                            |    |

| Table 3.9. Control Signal Timing Specifications                           | 19 |

| Table 3.10. ESD Specifications                                            | 19 |

| Table 5.1. HDMI Input Pins                                                |    |

| Table 5.2. HDMI Output Pins                                               |    |

| Table 5.3. External XTAL Pins                                             |    |

| Table 5.4. Control and Configuration Pins                                 | 22 |

| Table 5.5. Power and Ground Pins                                          | 23 |

| Table 5.6. Reserved and Not Connected Pins                                | 24 |

| Table 6.1. RGB to YCbCr Conversion mulas                                  | 25 |

| Table 6.2. YCbCr-to-RGB Conversion mulas                                  | 25 |

| Table 6.3. Supported HDMI 3D Input Video mats                             | 26 |

| Table 6.4. Control of I <sup>2</sup> C Address with CI2CA Signal          | 26 |

| Table 6.5. Control of I <sup>2</sup> C Address with GPIO4/GPIO5 Signal    | 27 |

|                                                                           |    |

# 1. General Description

The Sil9678 HDMI<sup>®</sup> transmitter is a High Definition Multimedia Interface (HDMI) transmitter. This transmitter supports HDMI 1.4 Specification on a wide range of BD/STB products.

The Sil9678 transmitter supports up to 4K x 2K video mat.

The Sil9678 transmitter supports High-bandwidth Digital Content Protection (HDCP) 2.2 Specification devices that require secure content delivery.

## 1.1. HDMI Input

- Supports 24/30/36-bit RGB/YCbCr 4:4:4/xvYCC, and 16/20/24-bit YCbCr 4:2:2 video input mats.

- Supports video mat up to 4K x 2K @

30 Hz RGB/YCbCr 4:4:4/YCbCr 4:2:2, and supports up to 4K x 2K @ 60Hz YCbCr 4:2:0.

- Supports 3D video mat up to 1080p @ 60 Hz.

- Supports high resolution VESA mode video mat up to QSXGA @ 60 Hz.

- Support HDCP 1.4.

- Low power 1.0 V core.

## 1.2. HDMI Output

- Supports HDCP 1.4 and HDCP 2.2.

- HDMI and DVI compatibility.

- HDMI Type A, Type C, and micro-D connector support.

#### 1.3. Features

- Supports HDMI 1.4 Specification.

- Supports HDCP 1.4/2.2 Specification.

- Supports color space conversions among RGB, YCbCr 4:4:4 and YCbCr 4:2:2 video mats without deep color.

- Supports color space conversions between RGB and xvYCC video mats without deep color.

## 1.4. Packaging

- 76-pin QFN (9 mm × 9 mm) package

- Standard part covers extended (-20 °C to +85 °C)

temperature range

Figure 1.1. Typical Application (Sil9678 HDMI Transmitter)

## 1.5. Pin Diagram

Figure 1.2 shows the pin assignments of the Sil9678 transmitter. Refer to the Pin Descriptions section beginning on page 21 describes the pin functions. The Sil9678 device is a 76-pin 9 mm × 9 mm QFN package with ePad, which *must* be connected to ground.

Figure 1.2. Pin Diagram (Top View)

# 2. Functional Description

The Sil9678 HDMI transmitter provides a complete solution transmitting ultra-high resolution (such as WQXGA, QSXGA, and 4K x 2K) with HDCP encryption. The Sil9678 transmitter can support HDMI output with HDCP 1.4 encryption or HDCP 2.2 encryption. Figure 2.1 shows the functional block diagram of the Sil9678 transmitter.

Figure 2.1. Functional Block Diagram

The Sil9678 HDMI transmitter provides an HDMI input interface. This interface supports TMDS clock speed up to 300 MHz. Refer to Table 2.1 supported 2D video mats. See the 3D Video mats section on page 26 the details of the supported 3D mats.

Table 2.1. Supported 2D Video mats

| 2D Video<br>Resolution      | Pixel mat          | Bus Width  | Maximum Frame Rate (Hz) |

|-----------------------------|--------------------|------------|-------------------------|

| VGA                         | RGB                | 24         | 60                      |

| WVGA                        | RGB                | 24         | 60                      |

| SVGA                        | RGB                | 24         | 60                      |

| XGA                         | RGB                | 24         | 60                      |

| SXGA                        | RGB                | 24         | 60                      |

| UXGA                        | RGB                | 24         | 60                      |

| WUXGA                       | RGB                | 24         | 60                      |

| QXGA                        | RGB                | 24         | 60                      |

| WQXGA                       | RGB                | 24         | 60                      |

| 480p/i                      | RGB<br>YCbCr 4:4:4 | 24, 30, 36 | 60                      |

|                             | YCbCr 4:2:2        | 16, 20, 24 |                         |

| <sup>1080</sup> ,<br>576p/i | RGB<br>YCbCr 4:4:4 | 24, 30, 36 | 50                      |

|                             | YCbCr 4:2:2        | 16, 20, 24 |                         |

| 720p                        | RGB<br>YCbCr 4:4:4 | 24, 30, 36 | 50/60                   |

|                             | YCbCr 4:2:2        | 16, 20, 24 |                         |

| 1080i                       | RGB<br>YCbCr 4:4:4 | 24, 30, 36 | 50/60                   |

|                             | YCbCr 4:2:2        | 16, 20, 24 |                         |

|                             | RGB                | 24, 30, 36 |                         |

|                             | YCbCr 4:2:2        | 16, 20, 24 |                         |

| 414 214                     | RGB<br>YCbCr 4:4:4 | 24         | 24/25/30                |

| 4K x 2K                     | YCbCr 4:2:2        | 16, 20, 24 |                         |

|                             | YCbCr 4:2:0        | 12         | 50/60                   |

#### Notes:

- 1. the 4K x 2K YCbCr 4:2:0 mat, no video data conversion is supported.

- 2. deep color mats, no video data conversion is supported.

## 2.2. Video Data Conversion Logic Block

The Sil9678 HDMI transmitter supports Video Data Conversion Logic Block. Figure 2.2 shows the processing stages the video data. Each of the processing blocks can be bypassed by setting the appropriate register bits.

The 4K x 2K YCbCr 4:2:0 @ 50/60 Hz video mat and deep color video mats are not supported in the Video Data Conversion Logic Block. Theree, these mats will be bypassed by this block automatically.

## 2.2.1. Color Space Converters

Color Space Converters (CSCs) are provided to convert RGB data to the Standard-Definition (ITU.601) or High-Definition (ITU.709) YCbCr mats, and vice-versa. To support the latest extended-gamut xvYCC displays, the Sil9678 device

implements color space converter blocks to convert RGB data to the extended-gamut Standard-Definition (ITU.601) or High-Definition (ITU.709) xvYCC mats, and viceversa. The CSC can be adjusted to perm standard-definition conversions (ITU.601) or high-definition conversions (ITU.709) by setting the appropriate registers.

See the RGB to YCbCr Color Space Converter and YCbCr to RGB Color Space Converter sections on page 25 more inmation.

#### 2.2.1.1. xvYCC Support

mat has roughly 1.8 times more colors than the RGB color space. The of the xvYCC color space is made possible the of the full range values (1 - 254) in an 8-bit space instead of 16 - 235 in the RGB mat.

#### 2.2.2. YCbCr Range Compression

When enabled by itself, the Range Compression Block compresses 0-255 full-range data into 16-235 limited-range data each video channel, and compresses to 16-240 the Cb and Cr channels. The color range scaling is linear.

#### 2.2.3. 4:4:4 to 4:2:2 Downsampler

Downsampling reduces the number of chrominance samples in each line by half, converting 4:4:4 sampled video to 4:2:2 video.

#### 2.2.4. 4:2:2 to 4:4:4 Upsampler

Chrominance upsampling and downsampling increase or decrease the number of chrominance samples in each line of video. Upsampling doubles the number of chrominance samples in each line, converting 4:2:2 sampled video to 4:4:4 sampled video.

#### 2.2.5. RGB Range Expansion

The Sil9678 device can scale the input color from limited-range into full-range using the range expansion block. When enabled by itself, the range expansion block expands 16 - 235 limited-range data into 0 - 255 each video channel. When the range expansion and the xvYCbCr/YCbCr to RGB color space converter are both enabled, the input conversion range the Cb and Cr channels is 16 - 240.

#### 2.2.6. 10 to 8 Bit Dither

The 10 to 8 Bit Dither block dithers ly-processed 10-bit data to 8-bit data output.

## 2.3. Receiver HDCP 1.4 Authentication Logic Block

The Receiver HDCP1.4 Authentication Logic Block handles the task of establishing a secure link receiving protected content from the source SoC. This process involves exchanging security inmation with the source SoC over the DDC.

## 2.4. HDCP 1.4 Decryption Engine Block

The HDCP1.4 Decryption Engine Block handles the task of decrypt data coming from the HDMI input interface. The appropriate decryption key is applied to the HDCP1.4 decryption engine block to descramble the video, audio, and

auxiliary packets.

## 2.5. Transmitter HDCP Authentication Logic Block

The Transmitter HDCP Authentication Logic Block handles the task of establishing a secure link transmitting protected content to downstream device. It also has two parts: one is HDCP 2.2 authentication, and the other is HDCP 1.4 authentication.

#### 2.6. HDCP 1.4/2.2Encryption Engine Block

Unlike the HDCP 1.x authentication, the authentication process HDCP 2.2 involves authentication and key exchange

(AKE), pairing downstream device, random number generation, locality check, and session key exchange (SKE). At the end of authentication, a communication path is established between the HDCP2.2 Transmitter and HDCP2.2 Receiver, to which authorized device can access.

The Sil9678 transmitter has two HDCP encryption engines: one is HDCP 2.2 encryption engine, the other is HDCP 1.4 encryption engine.

The HDCP encryption engine contains the logic necessary to encrypt the incoming audio and video data and includes support HDCP authentication check. The system microcontroller or microprocessor controls the encryption process by using a set sequence of register reads and writes.

## 2.7. HDMI TMDS Transmitter Block

The HDMI TMDS Transmitter Block can drive out a fully compliant HDMI stream, based on the specific registers settings through the API interface.

an HDMI stream, the video, audio, and auxiliary data are transmitted through three TMDS data channels along with a TMDS differential clock.

## 2.8. One-Time Programmable Block

The Sil9678 transmitter comes preprogrammed with a set of production HDCP keys stored in an ROM. System manufacturers do not need to purchase key sets from the Digital Content Protection LLC. handles all purchasing, programming, and security the HDCP keys. The preprogrammed HDCP keys provide the highest level of security beca there is no way to read the keys once the devices are programmed. Customers must sign the HDCP license agreement (www.digital-cp.com) or be under a specific NDA with bee receiving samples of the transmitter.

## 2.9. Serial Peripheral Interface Logic Block

The Serial Peripheral Interface (SPI) Logic Block provides an SPI Master interface. This SPI master interface is sampled once at reset to load the data from the external Flash/EEPROM when chip works in the stand-alone mode. Usually, the SPI master logic is disabled in the normal working mode, except when the ISP block is enabled. Refer to the In-System-Program Block section below more details.

## 2.10.In-System-Program Block

The Sil9678 transmitter supports In-System-Program (ISP) firmware upgrade. The firmware code is stored in the external Flash/EEPROM device that connected to the SPI interface. The ISP Block provides a connection between the Local I<sup>2</sup>C Slave Logic and the SPI Logic. With this ISP block, the external SoC can program the new code into the external Flash/EEPROM device directly through the local I<sup>2</sup>C slave interface.

## 2.11.Microcontroller Unit

implementation. It is d to control the main data flow byregister configuration and interrupt handling, as well as handle the initialization at reset, HDCP 1.4/2.2 authentication and encryption etc. This MCU will boot from the external Flash/EEPROM through the SPI master interface.

#### 2.12. Oscillator

The Sil9678 transmitter has an Oscillator (OSC) that provides the driving clock of the MCU

stand-alone mode. The frequency of this oscillator is 20MHz, which is calibrated in the factory. If oscillator is

## 2.13.Logic I<sub>2</sub>C Slave LogicBlock

The local I C slave bus provides a communication interface from the host to the Sil9678 device. The controller I C chosen, external crystal will not be needed. However, the MCU can the external crystal as the clock source and

disable the oscillator as well.

interface on the Sil9678 transmitter (signals CSCL and CSDA) is a slave interface capable of running up to 400 kHz. See parametric limitation above 100 kHz in Table 3.9 on page 19. The host s this interface to configure the Sil9678 transmitter by reading from and writing to appropriate registers.

I<sup>2</sup>C addresses of the device can be altered with the level of the CI2CA/GPIO4/GPIO5 signal, as described in the Device Address Configuration Using CI2CA/GPIO4/GPIO5 section on page 26.

## 2.14. Configuration, Status, and Interrupt Control Logic Block

The configuration block is d to configure and control the device operation, which can operate in either stand-alone mode (with MCU enabled) or in External MCU mode.

The Power-On Reset (POR) circuit is also contained in this block. POR provides an on-chip reset function to eliminate the need from an external POR circuit.

The level on INT pin is latched when the POR circuit transits from the asserted state to the de-asserted state. If the latched status is HIGH, the stand-alone mode will be selected. Otherwise, External MCU mode will be selected.

In the stand-alone mode, the Sil9678 chip requires an SPI flash/EEPROM firmware code storage and load the code to the MCU after the POR. All chip registers will be configured by the MCU. This mode supports ISP function firmware update.

In the External MCU mode, the Sil9678 chip requires an external I<sup>2</sup>C master such as MCU/SoC chip registers configuration or external Flash/EEPROM device programming with In-System-Program (ISP) block.

Figure 2.3 and Figure 2.4 show the connection of the local I<sup>2</sup>C port, SPI interface, and INT signal in stand-alone mode or in External MCU mode.

Figure 2.3. Stand-alone Mode

Figure 2.4. External MCU Mode

The INT signal interrupts the host processor when certain conditions arise inside the Sil9678 transmitter. The INT output is programmable to be either active HIGH or active LOW.

customers, an API adapter driver will be provided by hardware independent interface between the Sil9678 device and the customer application software. Refer to the Sil9678 API Reference (Sil-AR-1003) more details.

#### 2.15.DDC Slave Block

The Sil9678 transmitter s an HDMI source as the input source. The DDC Slave Block is d the HDMI source to read the EDID from the Sil9678 transmitter.

#### 2.16.DDC Master Block

The Sil9678 transmitter has a DDC Master the HDMI downstream device connection. The DDC master port is d direct connection to the HDMI cable. DDC read and write operations are executed by reading and writing registers in the transmitter. This feature simplifies the system design and helps to lower its cost.

## 2.17.On-Chip Regulation

The on-chip regulators provide a low-cost system implementation. The Sil9678 transmitter has two regulators: 3.3 V Regulator and 1.2 V Regulator. Both regulators are provided usage.

Each of the regulators has one output pin. The output pins are VDD33OUT and VDD12OUT. All these pins cannot be d as any external power supply, but require a separate 4.7 μF capacitor to ground each of the pin.

# 3. Electrical Specifications

## 3.1. Absolute Maximum Conditions

**Table 3.1. Absolute Maximum Conditions**

| Symbol           | Parameter                                  | Min  | Тур | Max           | Units | Notes   |

|------------------|--------------------------------------------|------|-----|---------------|-------|---------|

| XTAL_VDD33       | XTAL Power Supply                          | -0.3 | _   | 4.0           | V     | 1, 2    |

| VDD33            | 3.3 V Analog Power Supply                  | -0.3 | _   | 4.0           | V     | 1, 2    |

| VDDIO33          | Digital I/O Power Supply                   | -0.3 | _   | 4.0           | V     | 1, 2    |

| AVDD33           | Analog Driver Power Supply                 | -0.3 | _   | 4.0           | V     | 1, 2    |

| VDD10            | Digital Core Power Supply                  | -0.3 | _   | 1.25          | V     | 1, 2    |

| AVDD10           | Analog Receiver PHY Power Supply           | -0.3 | _   | 1.25          | V     | 1, 2    |

| AVDD10_PLL       | Analog PLL Power                           | -0.3 | _   | 1.25          | V     | 1, 2    |

| AVDD10_DP        | Analog Data Path Power                     | -0.3 | _   | 1.25          | V     | 1, 2    |

| AVDD10_OSC       | Power Supply of Oscillator                 | -0.3 | _   | 1.25          | V     | 1, 2    |

| FVDD10           | Fractional PLL Power                       | -0.3 | _   | 1.25          | V     | 1, 2    |

| RPWR5V           | 5 V Input from Power Pin of HDMI Connector | -0.3 | _   | 5.7           | V     | 1, 2    |

| VDD5V_IN         | Local Power 5 V Input                      | -0.3 | _   | 5.7           | V     | 1, 2    |

| LPSBV5V          | Low Power Standby 5 V Input                | -0.3 | _   | 5.7           | V     | 1, 2    |

| VI               | Input Voltage                              | -0.3 | - 1 | VDDIO33 + 0.3 | V     | 1, 2    |

| Vo               | Output Voltage                             | -0.3 | -   | VDDIO33 + 0.3 | V     | 1, 2    |

| V <sub>I5V</sub> | Input Voltage, 5 V Tolerant I/O            | -0.3 | _   | 5.5           | V     | 1, 2, 4 |

| V <sub>05V</sub> | Output Voltage, 5 V Tolerant I/O           | -0.3 | _   | 5.5           | V     | 1, 2, 4 |

| Tj               | Junction Temperature                       |      | _   | 125           | °C    | _       |

| T <sub>STG</sub> | Storage Temperature                        | -65  | _   | 150           | °C    | _       |

#### Notes:

- 1. Permanent device damage can occur if absolute maximum conditions are exceeded.

- 2. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

- 3. Voltage undershoot or overshoot cannot exceed absolute maximum conditions.

- 4. This is 5V tolerant pins, such as TX \_HPD, RX HPD, DSCL, DSDA, INT, TDSCL, TDSDA, CSCL, CSDA, GPIO0, GPIO1, GPIO2,

GPIO3, GPIO4, and GPIO5.

## 3.2. Normal Operating Conditions

**Table 3.2. Normal Operating Conditions**

| Symbol          | Parameter                                  | Min  | Тур     | Max  | Unit              | Notes |

|-----------------|--------------------------------------------|------|---------|------|-------------------|-------|

| XTAL_VDD33      | XTAL Power Supply                          | 3.13 | 3.3     | 3.47 | V                 | _     |

| VDD33           | 3.3 V termination Power Supply             | 3.13 | 3.3     | 3.47 | V                 | 1     |

| VDDIO33         | Digital I/O Power Supply                   | 3.13 | 3.3     | 3.47 | V                 | _     |

| AVDD33          | Analog Driver Power Supply                 | 3.13 | 3.3     | 3.47 | V                 | _     |

| VDD10           | Digital Core Power Supply                  | 0.95 | 1.0     | 1.05 | V                 | _     |

| AVDD10          | Analog Receiver PHY Power Supply           | 0.95 | 1.0     | 1.05 | V                 |       |

| AVDD10_PLL      | Analog PLL Power                           | 0.95 | 1.0     | 1.05 | V                 | _     |

| AVDD10_DP       | Analog Data Path Power                     | 0.95 | 1.0     | 1.05 | V                 | _     |

| _AVDD10_OSC     | Power Supply of Oscillator                 | 0.95 | 1.0     | 1.05 | V                 |       |

| FVDD10          | Fractional PLL Power                       | 0.95 | 1.0     | 1.05 | V                 | _     |

| RPWR5V          | 5 V Input from Power Pin of HDMI Connector | 4.3  | 5.0     | 5.25 | V                 | _     |

| VDD5V_IN        | Local Power 5 V Input                      | 4.3  | 5.0     | 5.25 | V                 | _     |

| LPSBV5V         | Low Power Standby 5 V Input                | 4.75 | 5.0     | 5.25 | V                 | _     |

| V<br>DDN        | Allowable Supply Voltage Noise             | _    | _       | 100  | mV <sub>P-P</sub> | 2     |

| TA              | Ambient Temperature (with power applied)   | -30  | 25      | 85   | °C                | _     |

| Θ<br>ja         | Ambient Thermal resistance (Theta JA)      | _    | _       | 28.0 | °C/W              | 3     |

| Θ <sub>jc</sub> | Ambient Thermal resistance (Theta JC)      |      | <u></u> | 14.4 | °C/W              | 3     |

#### Notes:

- 1. The HDMI Specification requires 3.3 V ±5% termination voltage (VDD33).

- The supply voltage noise is measured in testing point VDDTP as shown in Figure 3.1. The ferrite bead provides filtering of power supply noise.

- 3. Values  $\Theta_{ja}$  and  $\Theta_{jc}$  are provided fpr 4-layer PCB, Airflow at 0 m/s.

#### VDD

See the Power Supplies Decoupling section on page 28 the recommended decoupling and power supply regulation.

# Ferrite 10 μF 2.2 μF 0.1 μF 0.01 μF SiI9678 GND

Figure 3.1. Test Point VDDTP VDD Noise Tolerance Specification

## 3.2.1. Digital I/O Specifications

Under normal operating conditions unless otherwise specified.

Table 3.3. DC Digital I/O Specifications

| Symbol                                  | Parameter                                      | Pin Type            | Conditions              | Min | Тур  | Max | Units | Notes   |

|-----------------------------------------|------------------------------------------------|---------------------|-------------------------|-----|------|-----|-------|---------|

| V <sub>IH</sub>                         | HIGH Level Input Voltage                       | LVTTL               | _                       | 2.0 | _    | _   | V     | 2       |

| V <sub>IL</sub>                         | LOW Level Input Voltage                        | LVTTL               | _                       | _   | _    | 0.8 | V     | 2       |

| V<br>TH+DDC                             | LOW to HIGH Threshold,<br>DDC bus              | Schmitt             | -                       | 3.5 | _    | _   | V     | 5, 8    |

| V<br>TH-DDC                             | HIGH to LOW Threshold<br>DDC bus               | Schmitt             | _                       | _   | _    | 1.5 | V     | 5, 8    |

| V<br>TH+RESETN                          | LOW to HIGH threshold,<br>RESETN pin           | Schmitt             | _                       | 2.0 | _    | _   | V     | _       |

| V<br>TH-RESETN                          | HIGH to LOW threshold,<br>RESETN pin           | Schmitt             | _                       | _   | _    | 0.8 | V     | _       |

| V<br>TH+I2C                             | LOW to HIGH Threshold,<br>I <sup>2</sup> C Bus | Schmitt             | _                       |     | 2.0— | _   | V     | -       |

| V<br>TH-I2C                             | HIGH to LOW Threshold,<br>I <sup>2</sup> C Bus | Schmitt             | _                       | _   | _    | 0.8 | V     | ı       |

| V                                       | HIGH Level Output<br>Voltage                   | LVTTL<br>Open Drain | IOH = 3 mA              | 2.4 | _    | _   | V     | _       |

| V <sub>OL</sub>                         | LOW Level Output<br>Voltage                    | LVTTL<br>Open Drain | I <sub>OL</sub> = 3 mA  | _   | _    | 0.4 | V     | _       |

| I /I<br>IL IH                           | Input Leakage Current                          | _                   | _                       | -10 | _    | 10  | μΑ    | -       |

| TX_HPD I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current                          | _                   | _                       | -30 | _    | 30  | μΑ    | _       |

| l<br>OD                                 | General Digital Output                         | Output              | V <sub>он</sub> = 2.4 V | 7.5 | _    | _   | mA    | 1, 6, 7 |

|                                         | Drive                                          |                     | <sup>V</sup> OL = 0.4 V |     | _    | _   | mA    | 1, 6, 7 |

#### Notes:

- 1. These limits are guaranteed by design.

- 2. Under normal operating conditions unless otherwise specified, including output pin loading  $C_L = 10 \text{ pF}$ .

- 3. Refer to the Pin Descriptions section on page 21 pin type designations all package pins.

- 4. Differential input voltage is a single-ended measurement, according to the DVI Specification.

- 5. these Schmitt trigger input pin thresholds  $V_{TH+}$  and  $V_{TH-}$  correspond to  $V_{IH}$  and  $V_{IL}$ , are respectively guaranteed by design.

- 6. Minimum output drive specified at ambient = 70 °C and VDD33 = 3.0 V. Typical output drive specified at ambient = 25 °C and VDD33 = 3.3 V. Maximum output drive specified at ambient = -20 °C and VDD33 = 3.6 V.

- 7. IOD Output applies to all pins defined as LVTTL and LVTTL/Schmitt trigger.

- 8. IODDDC Output applies to all pins defined as Schmitt trigger.

#### **Table 3.4. TMDS Input DC Specification**

| Symbol   | Parameter                             | Conditions | Min         | Тур | Max          | Units |

|----------|---------------------------------------|------------|-------------|-----|--------------|-------|

| V<br>IDF | Differential Mode Input Swing Voltage | 1          | 150         | -   | 1200         | mV    |

| ICM      | Common Mode Input Swing Voltage       | _          | VTERM - 400 | _   | VTERM - 37.5 | mV    |

#### **Table 3.5. TMDS Output DC Specifications**

| Symbol | Parameter                              | Conditions          | Min          | Тур | Max          | Units |

|--------|----------------------------------------|---------------------|--------------|-----|--------------|-------|

| VSWING | Single-ended Output Swing Voltage      | RLOAD = $50 \Omega$ | 400          | -   | 600          | mV    |

| VH     | Single-ended HIGH-level Output Voltage | _                   | AVDD33 – 200 | _   | AVDD33 + 10  | mV    |

| VL     | Single-ended LOW-level Output Voltage  | -                   | AVDD33 – 700 | -   | AVDD33 – 400 | mV    |

## 3.2.2. DC Power Consumption

**Table 3.6. DC Power Consumption**

| Symbol           | Parameter          | Output       | Typical |       |       | Maximum |        |       | Units | Notes |

|------------------|--------------------|--------------|---------|-------|-------|---------|--------|-------|-------|-------|

| Syllibol         | raiailletei        | Frequency    | 5 V     | 3.3 V | 1.0 V | 5.5 V   | 3.63 V | 1.1 V | Units | Notes |

| <b> </b><br>DDSB | Standby<br>Current | _            | 7.2     | 8.9   | 133   | 8.4     | 9.1    | 195   | mA    | 1     |

|                  | Full               | 720x480p60   | 7.3     | 53.9  | 165   | 8.4     | 54.5   | 259   | mA    | 2     |

| DDFP             | Operation          | 1920x1080p60 | 7.3     | 53.5  | 200   | 8.4     | 54.1   | 312   | mA    | 2     |

|                  | Current            | 4Kx2Kp30     | 7.3     | 52.9  | 272   | 8.4     | 53.5   | 414   | mA    | 2     |

#### Notes:

- 1. All power nets are supplied and no input and output are connected.

- 2. Test results will differ pending on TMDS driving current settings of the HDMI source.

# 3.3. AC Specification

Differential Input Clock Jitter Tolerance

165 MHz-

## 3.3.1. TMDS AC Timing Specifications

Under normal operating conditions unless otherwise specified.

**Table 3.7. TMDS Input Timing AC Specifications**

| Symbol                       | Parameter                          | Conditions | Min  | Тур | Max                     | Units     |

|------------------------------|------------------------------------|------------|------|-----|-------------------------|-----------|

| T<br>INTRA-PAIR SKEW         | Input Intra-pair Skew              | _          |      |     | 0.4                     | Т         |

| T <sub>INTER-PAIR_SKEW</sub> | Input Inter-pair Skew              | _          | _    |     | 0.4<br>0.2TpiXEL + 1.78 |           |

| F                            | 5.6                                |            | 25   |     | 300                     | ns<br>MHz |

| RXC                          | Differential Input Clock Frequency | _          | 25   |     | 40                      | ns        |

| T                            | Differential Input Clock Period    | _          | 3.33 |     | 0.3                     | T         |

|                              |                                    |            |      |     | 0.3                     | DII       |

**Table 3.8. TMDS Output Timings**

| 1 4516 3.0. 11 | VIDS Output Tillings                 | T          | May  | Units |      |     |

|----------------|--------------------------------------|------------|------|-------|------|-----|

| Symbol         | Parameter                            | Conditions | Min  | Тур   | Max  | T   |

| TXDPS          | Intra-Pair Differential Output Skew  | _          | _    | _     | 0.15 | BIT |

| 17,51.5        |                                      |            |      | _     | _    | ps  |

| T              | Data/Clock Rise Time                 | _          | 75   | _     | -    | ps  |

| T              | Data/Clock Fall Time                 | _          | 75   | _     | 300  | MHz |

| F              | Differential Output Clock Frequency  | _          | 25   | _     | 40   | ns  |

| T              |                                      | _          | _    |       |      | T   |

| T TXC          | Differential Output Clock Period     | _          | 3.33 | _     | 60   | TXC |

| DUTY           | Differential Output Clock Duty Cycle | _          | 40   |       | 0.25 | BIT |

| TILO           | Differential Output Clock Jitter     | _          | _    |       |      | •   |

## 3.3.2. Control Signal Timing Specifications

Under normal operating conditions unless otherwise specified.

**Table 3.9. Control Signal Timing Specifications**

| Symbol                          | Parameter                                                                                                | Conditions               | Min | Тур | Max | Units | Figure     | Notes |

|---------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|-----|-------|------------|-------|

| T<br>RESET_VDD                  | Time required RESETN high bee VDD                                                                        | 50% RESETN to<br>90% VDD | 1   | -   | _   | μs    | Figure 4.1 | _     |

| T<br>RESET                      | RESETN signal LOW time required reset                                                                    | _                        | 2   | _   | _   | ms    | Figure 4.2 | 1, 5  |

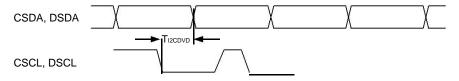

| T<br>I2CDVD                     | SDA data valid delay from SCL falling edge on READ command                                               | C <sub>L</sub> = 400 pF  | _   | _   | 700 | ns    | Figure 4.3 | 2, 6  |

| T<br>HDDAT                      | I <sup>2</sup> C data hold time                                                                          | 0 – 400 kHz              | 2.0 | _   | _   | ns    | _          | 3, 6  |

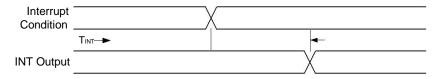

| T                               | Response time INT output signal from change in input condition (HPD, Receiver Sense, VSYNC Change etc.). | RESETN = HIGH            | _   | _   | 100 | μs    | Figure 4.4 | _     |

| F<br>TDSCL                      | Frequency of DDC master TDSCL signal                                                                     | _                        | 40  | 70  | 100 | kHz   | _          | 4     |

| F CSCL levels, I'C speeds up to | Frequency of local I <sup>2</sup> C CSCL signal                                                          | _                        | 40  | _   | 400 | kHz   | _          | _     |

#### Notes:

- 1. Reset on RESETN signal can be LOW as the supply becomes stable, as shown in Figure 4.1, or pulled LOW at least TRESET as shown in Figure 4.2.

- 2. All standard-mode (100 kHz) I<sup>2</sup>C timing requirements are guaranteed by design. These timings apply to the slave I<sup>2</sup>C port (pins CSDA and CSCL) and to the master I<sup>2</sup>C port (pins DSDA and DSCL).

- 3. This minimum hold time is required by CSCL and CSDA signals as an I<sup>2</sup>C slave. The device does not include the 300 ns delay required by the I<sup>2</sup>C Specification.

- 4. The DDC master block provides a TDSCL signal the transmitter DDC bus. The HDMI Specification limits this to I<sup>2</sup>C Standard

- Mode or 100 kHz. of the Master DDC block does not require an active IDCK.

- 5. Not a Schmitt trigger.

- 6. Operation of I<sup>2</sup>C pins above 100 kHz is defined by LVTTL levels ViH, ViL, VoH, and VoL. See Table 3.3 on page 17. these

## 3.3.3. ESD Specifications

**Table 3.10. ESD Specifications**

| Symbol   | Parameter                          | Min   | Тур | Max | Units | Notes |

|----------|------------------------------------|-------|-----|-----|-------|-------|

|          |                                    |       |     |     |       |       |

|          |                                    |       |     |     |       |       |

| 2. Measu | red according to JESD78B standard. |       |     |     |       |       |

| Latch up | ESD Latch up                       | ± 200 | _   |     | mA    | 1, 2  |

| НВМ      | Human Body Model                   | 2000  | _   | _   | V     | 3     |

| CDM      | Charged Device Model               | 500   | _   | _   | V     | 5     |

#### Notes:

- Test is permed at 70 °C.

- 3. Measured according to JESD22-A114 standard.

- 4. Measured according to JESD22-A115 standard.

- 5. Measured according to JESD22-C101 standard.

## 4. Timing Diagrams

## 4.1. RESETTN Timing Diagrams

Power sequencing is not required the Sil9678 transmitter. However, to ensure a proper reset the rules mentioned under the diagrams in Figure 4.1 and Figure 4.2 must be followed.

VDD10 must be stable between its limits Normal Operating Conditions T<sub>RESET\_VDD</sub> bee RESETN goes high, as shown in Figure 4.1. Bee accessing registers, RESETN must be pulled low T<sub>RESET</sub>. This can be done by holding RESETN low until T<sub>RESET\_VDD</sub> after stable power, as described above, or by pulling RESETN low from a high state at least T<sub>RESET</sub>, as shown in Figure 4.2.

Figure 4.1. Conditions of RESETN

Figure 4.2. RESETN Minimum Timings

## 4.2. Output Timing Diagrams

Figure 4.3. I<sup>2</sup>C Data Valid Delay (Driving Read Cycle Data)

Figure 4.4. INT Output Signal Response to Interrupt Condition

# 5. Pin Descriptions

The following tables provide the pin descriptions the Sil9678 transmitter.

# 5.1. HDMI Input

**Table 5.1. HDMI Input Pins**

| Pin Name | Pin | Туре         | Dir                                                 | Description                                                    |

|----------|-----|--------------|-----------------------------------------------------|----------------------------------------------------------------|

| RXCN     | 7   | TMDS         | Input                                               | LIDNAL Differential Clock Input                                |

| RXCP     | 8   | TMDS         | Input                                               | HDMI Differential Clock Input.                                 |

| RXON     | 11  | TMDS         | Input                                               | HDMI Differential Channel 0 Data Input.                        |

| RX0P     | 12  | TMDS         | Input                                               | ndivii dinerentiai Chamero data input.                         |

| RX1N     | 13  | TMDS         | Input                                               | LIDNAL Differential Channel 1 Data Innut                       |

| RX1P     | 14  | TMDS         | Input                                               | HDMI Differential Channel 1 Data Input.                        |

| RX2N     | 15  | TMDS         | Input                                               |                                                                |

| RX2P     | 16  | TMDS         | Input                                               | HDMI Differential Channel2 Data Input.                         |

| RX_HPD   | 4   | 5 V tolerant | Output                                              | HPD (Hot-plug Detect) Output of HDMI RX side.                  |

|          |     | Schmitt      |                                                     |                                                                |

| DSCL     | 75  | 5 V tolerant | Input                                               | DDC Clock and Data of HDMI RX side.                            |

|          |     | Open-drain   |                                                     | These signals are true open-drain, and do not pull to ground   |

|          |     | Schmitt      | when power is not applied to the device. These pins | when power is not applied to the device. These pins require an |

| DSDA     | 76  | 5 V tolerant | Input/                                              | external pull-up resistor.                                     |

|          |     | Open-drain   | Output                                              |                                                                |

## 5.2. HDMI Output

**Table 5.2. HDMI Output Pins**

| Pin Name | Pin | Туре                                  | Dir                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----|---------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXCN     | 40  | TMDS                                  | Input                                     | HDMI Differential Clock Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXCP     | 41  | TMDSInput                             |                                           | The state of the s |

| TX0N     | 42  | TMDS                                  | Input                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TX0P     | 43  | TMDS                                  | Input                                     | HDMI Differential Channel 0 Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX1N     | 44  | TMDS                                  | Input                                     | HDMI Differential Channel 1 Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX1P     | 45  | TMDS                                  | Input                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TX2N     | 46  | TMDS                                  | Input HDMI Differential Channel 2 Output. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TX2P     | 47  | TMDS                                  | Input                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TX_HPD   | 38  | 5 V tolerant                          | Input                                     | Hot-plug Detect Input. An external 10 $k\Omega$ pull-down resistor is required on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |